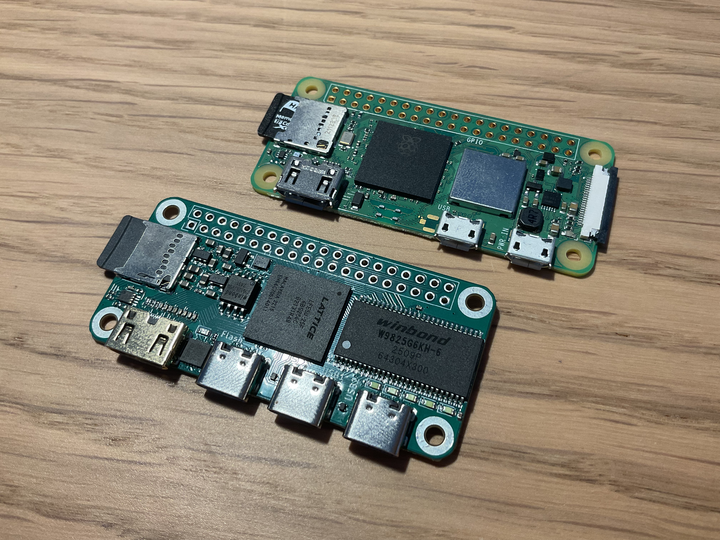

Icepi Zero - Raspberry Pi Zero FPGA Equivalent

Your portable FPGA in a Raspberry Pi Zero form (OSHWA certified! 450+ Github stars, entire dev batch sold for 200$)

Followers

krunch

Check their project out: Raspberry Pi Tinker HAT

cskartikey

Check their project out: The Journey

ShyMike

Check their project out: Hackatime Analyzer

Neon

Check their projects out: Hacker news checker, Market , Artophage, Slack - Zeon

sonicx180

Whoops! Looks like they don't have a project yet. Maybe ask them to start one?

Shibam Roy

Check their project out: Shibam's portfolio

Praveenkushinpi

Check their project out: ZenZ

TheTridentGuy

Check their project out: TLS like it's 1969

Mikolaj

Check their project out: GitForest

Navdeep

Check their projects out: Cryptonium, Arena, Scribbly, UwU

Irtaza

Check their projects out: NanoDeck, PokéDeck + Custom OS

FaizaanTheRealOne

Check their projects out: Personal Portfolio UPDATE, Personal Portfolio UPDATE

Hat Dealer

Check their project out: VoxaEngine - C++ SDL2 Voxel Engine

Tetie

Check their project out: babble (database)

yessa

Check their project out: starter pack

Gizzy (No.1 PHP Hater)

Check their project out: EdulinkAPK

Lukas

Check their projects out: 40%ish split keyboard Case & Code, Update my Website!!!

manni

Check their projects out: Mannuino, My personal website, Mouse

Chris

Check their project out: Strings

endercass

Check their project out: anuraOS Tadpole

virtualfuzz

Check their project out: rivulet_auth - authentication framework/server

Aahil

Check their project out: LED Memory Game Arduino Nano

Waddle_Penguin

Check their project out: Star Wars Sabbac Website

Sahil

Check their project out: make a website and make jekyll theme to test the jekyll theme on the website.

Akaalroop

Check their project out: Space Dodge (Website)

Pat/Patcybermind

Whoops! Looks like they don't have a project yet. Maybe ask them to start one?

krn

Check their project out: Inky; rpi camera but in an awesome case

felix

Check their project out: Chronoelegy

Pegoku

Check their projects out: Home Assistant Control pad, Shipfinity YSWS

StrawberryPuding

Check their project out: Terminal plotter

Nicholas West

Whoops! Looks like they don't have a project yet. Maybe ask them to start one?

anne

Check their projects out: anneOS | personal website, sorceline | custom cyberdeck workstation, inquill | custom pen plotter

Evan Yu

Check their project out: Scribe

m5kro

Check their project out: HTML Tools

Hashim

Check their project out: 3D Portfolio

Souptik Samanta

Whoops! Looks like they don't have a project yet. Maybe ask them to start one?

Ship Your Project

HOLD UP

By shipping your project, you're marking it as complete and it'll enter matchmaking. However, you will NOT be able to edit it anymore.

Timeline

Updates:

Reflashed firmware

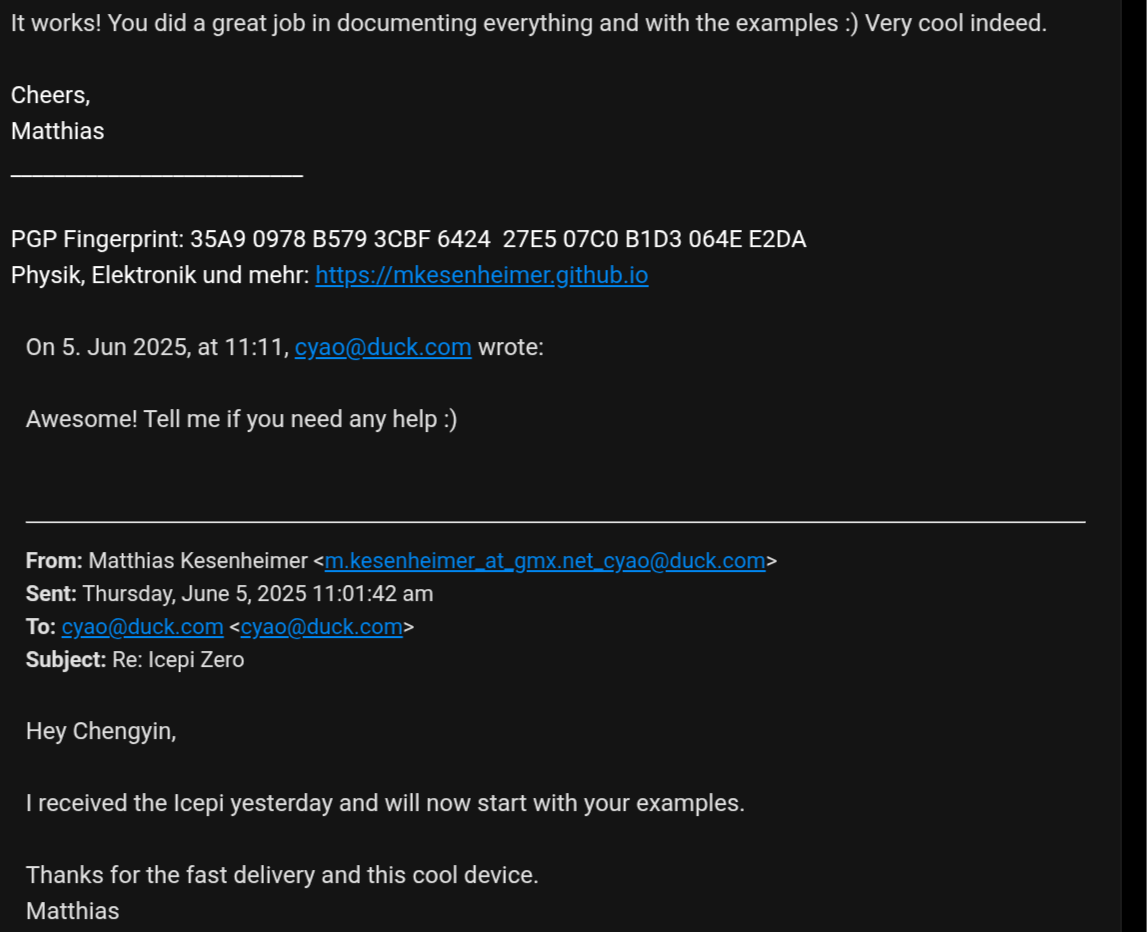

Customers received icepis, they are happy :yay:

updated project banner

worked more on dvi/hdmi, this still isn't working ugghhhhhhhhhhhhhhhhhh

Work done:

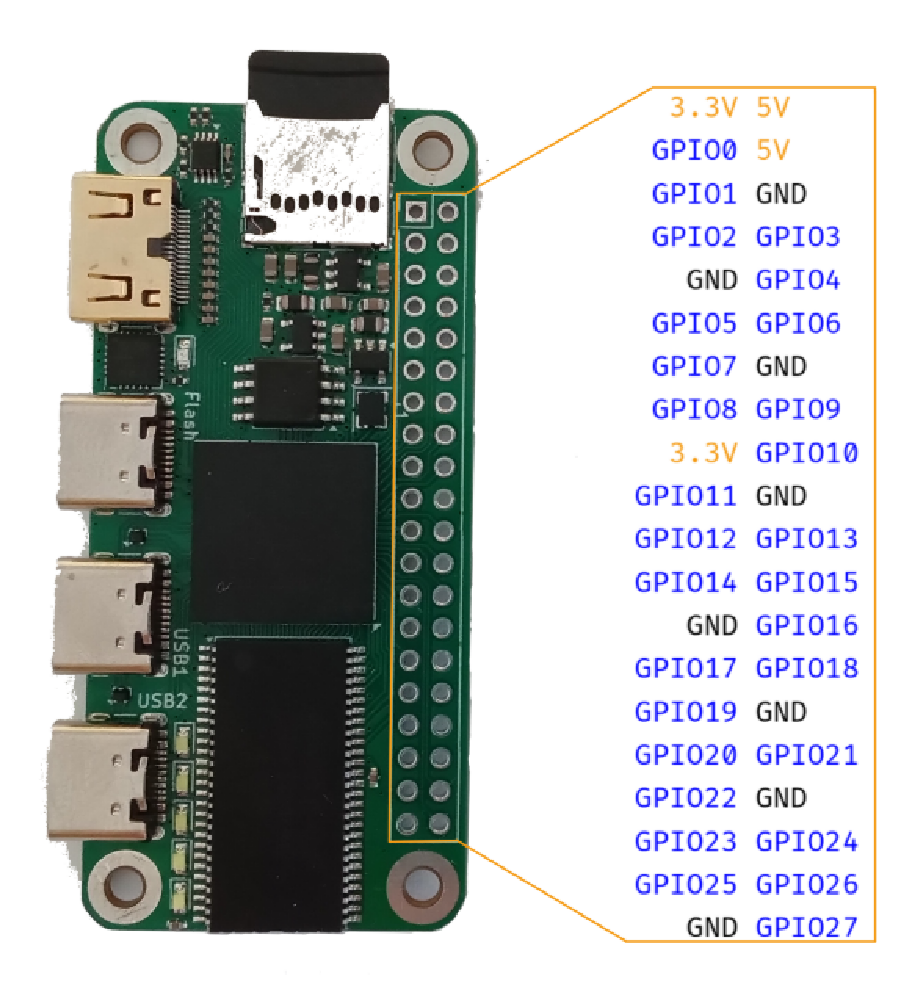

Pinout diagram made

My project is OSHWA certified! It's now a true open source hardware project https://certification.oshwa.org/fr000026.html

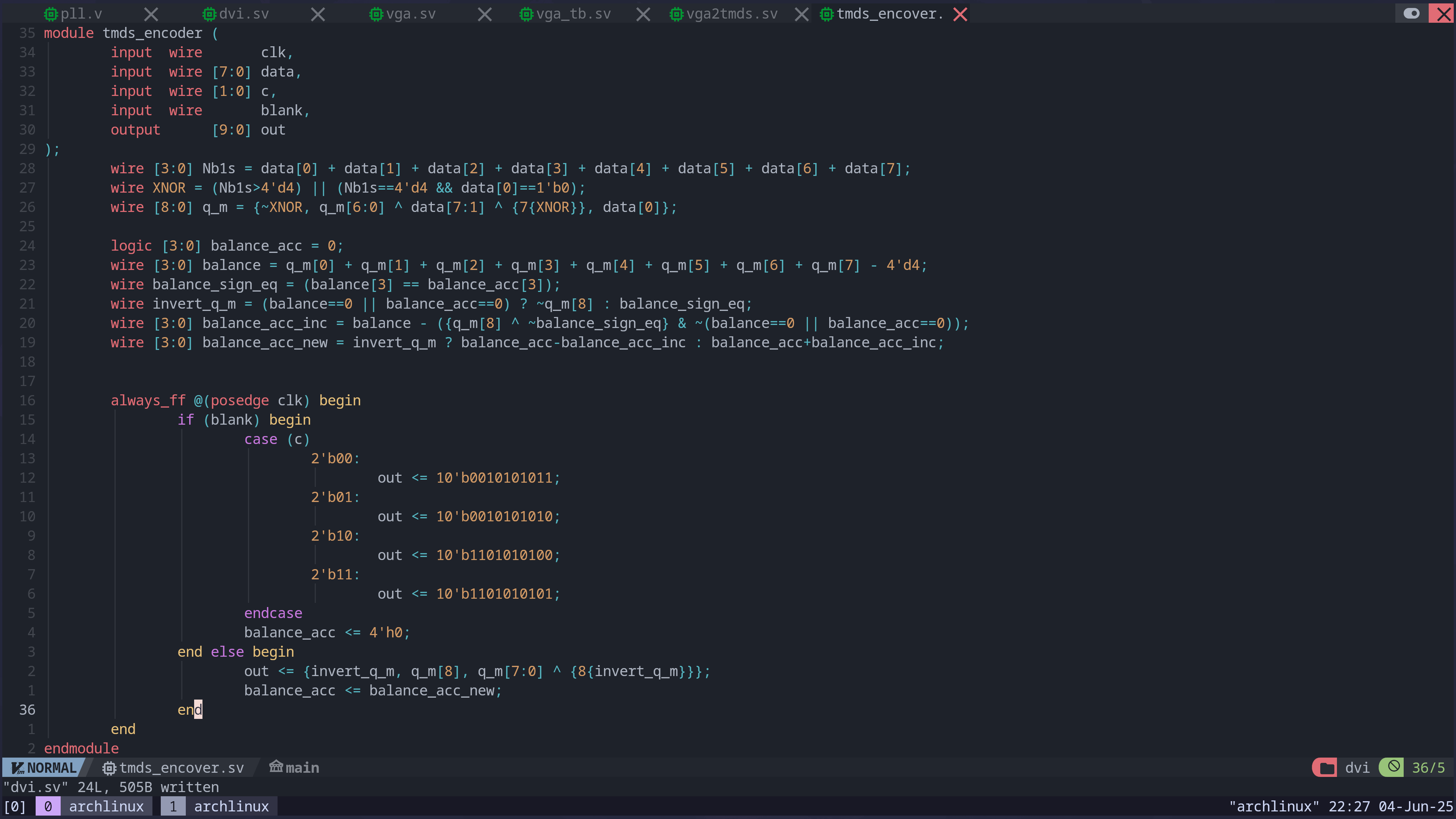

Continued implementing HDMI (DVI via tmds).

This is soooooooo complex. The TMDS protocol is cursed. Had to do extensive searching and waveform debugging

Dug into ECP5 PLL generation in order to generate my HDMI clock, buuut it's super undocumented and requires quite a lot of maths stuff.... Also made the start of my VGA code!

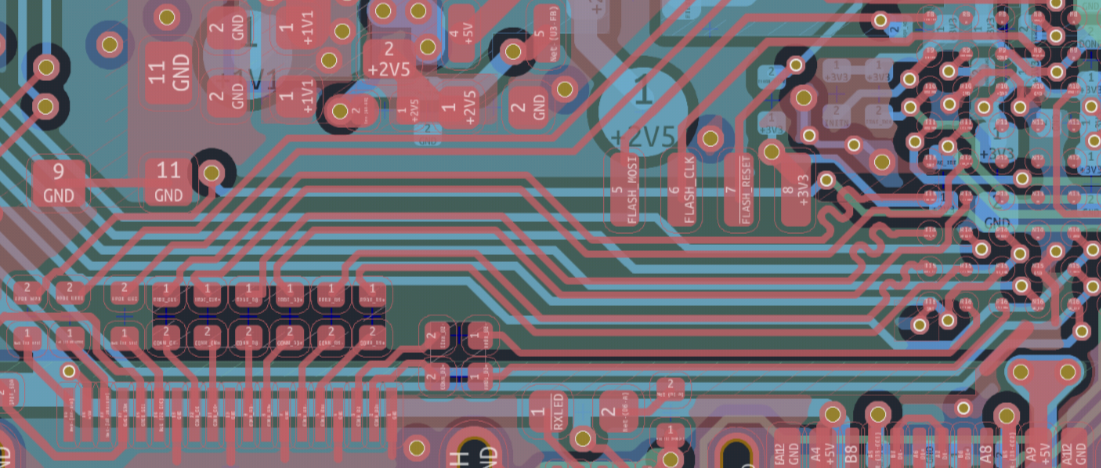

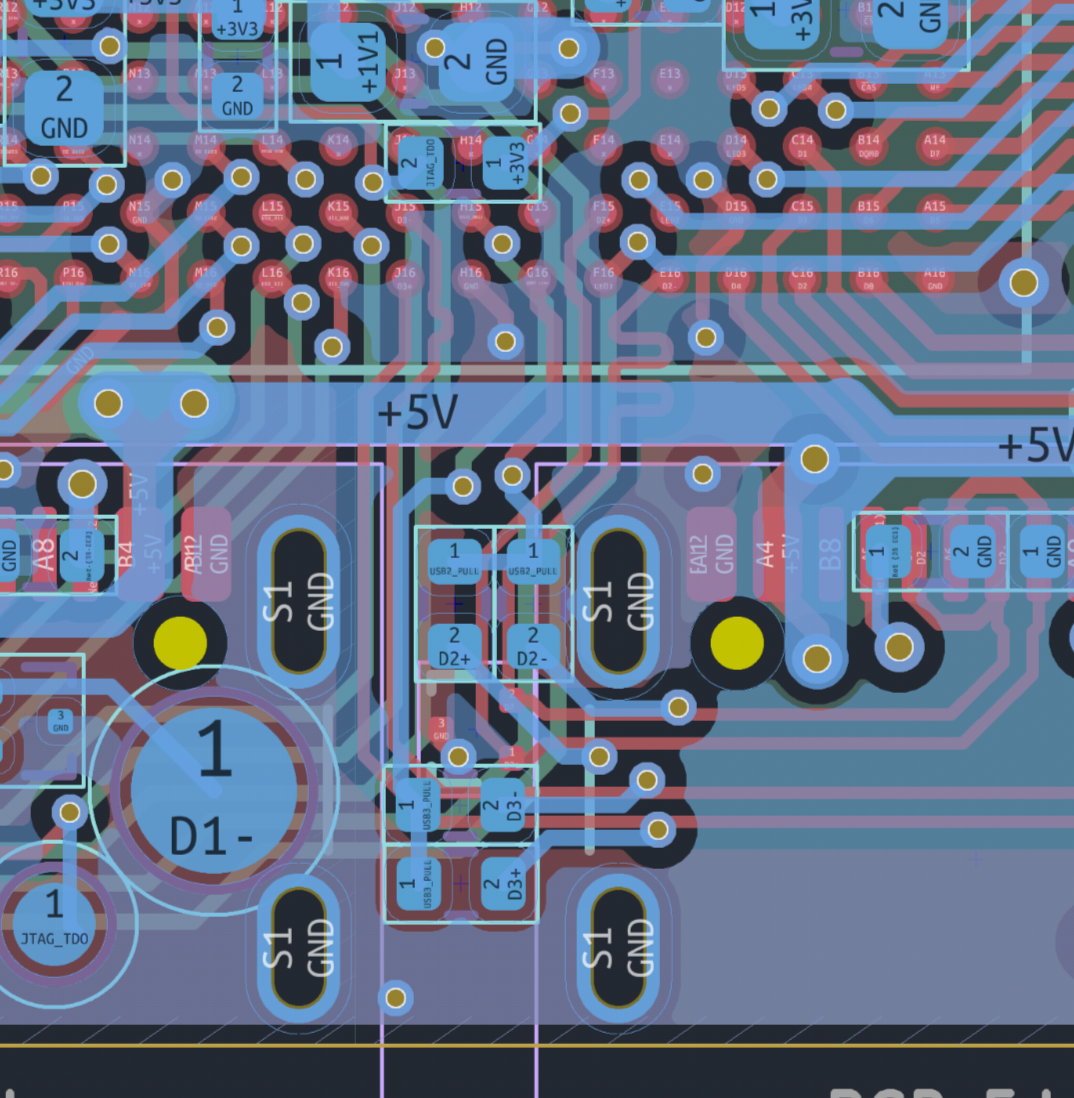

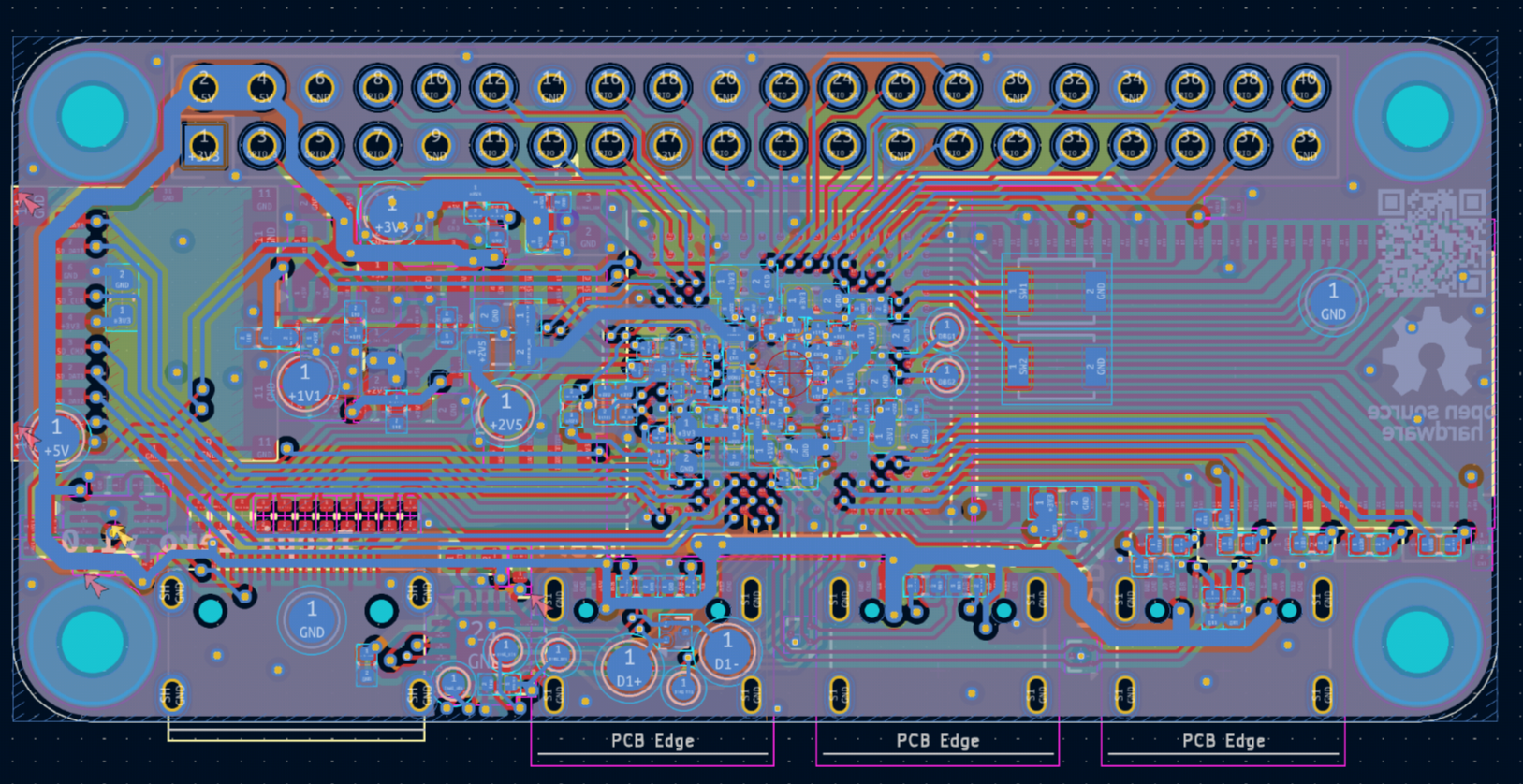

Redid the HDMI routing!

Now this is much better: It respects the rule of 3! Also the impedance is matched to the HDMI spec, the inter and intra pair skew respected.

USB impedance recalculated too!

Also some misc fixes!

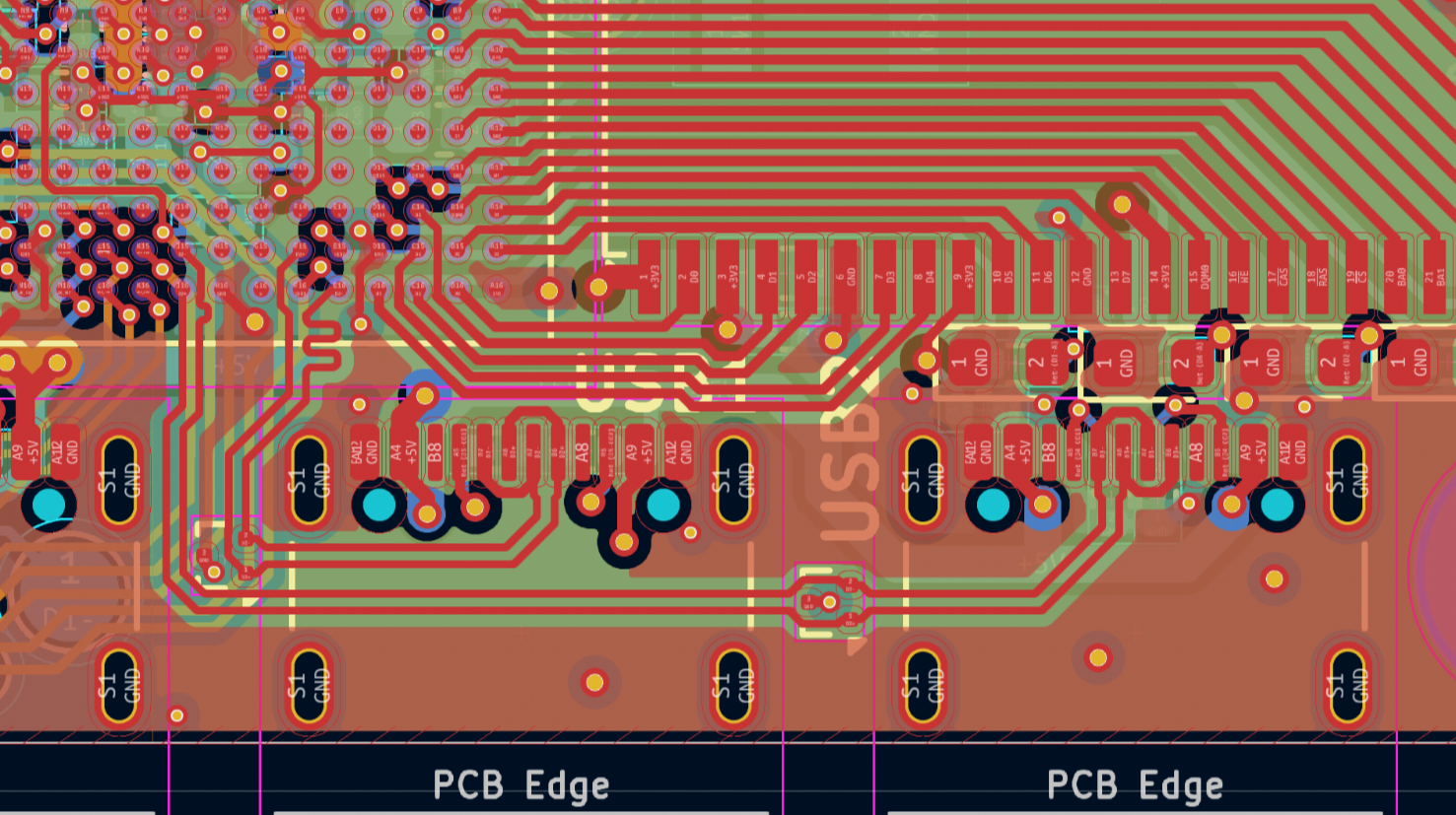

Optimized the routing of a few things:

Left side level shifter

The USB pull resistor & io traces

Improved gnd plane integraty

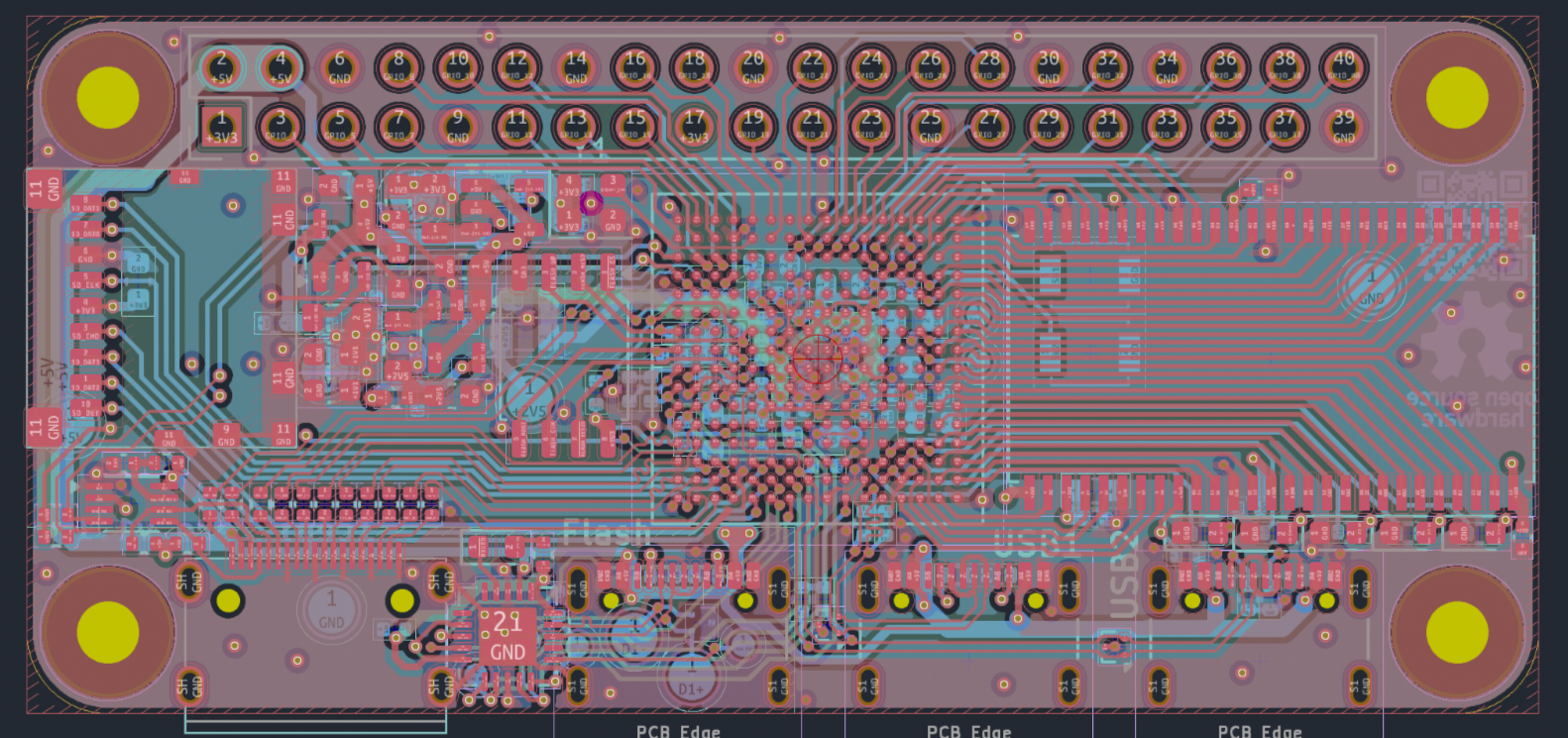

Next step: OSHW certification!

Tried to redo HDMI routing, but decided that my old one was good

- Updated firmware docs

- Responded to elecrow email

- Got 300+ stars!!!

you are doing great watching all those stars and USB-C feels which most of SOC's lack in best of luck Cyao

Updates:

1. Fixed gerber files not on github

2. Pushed a few fixes onto the github repo

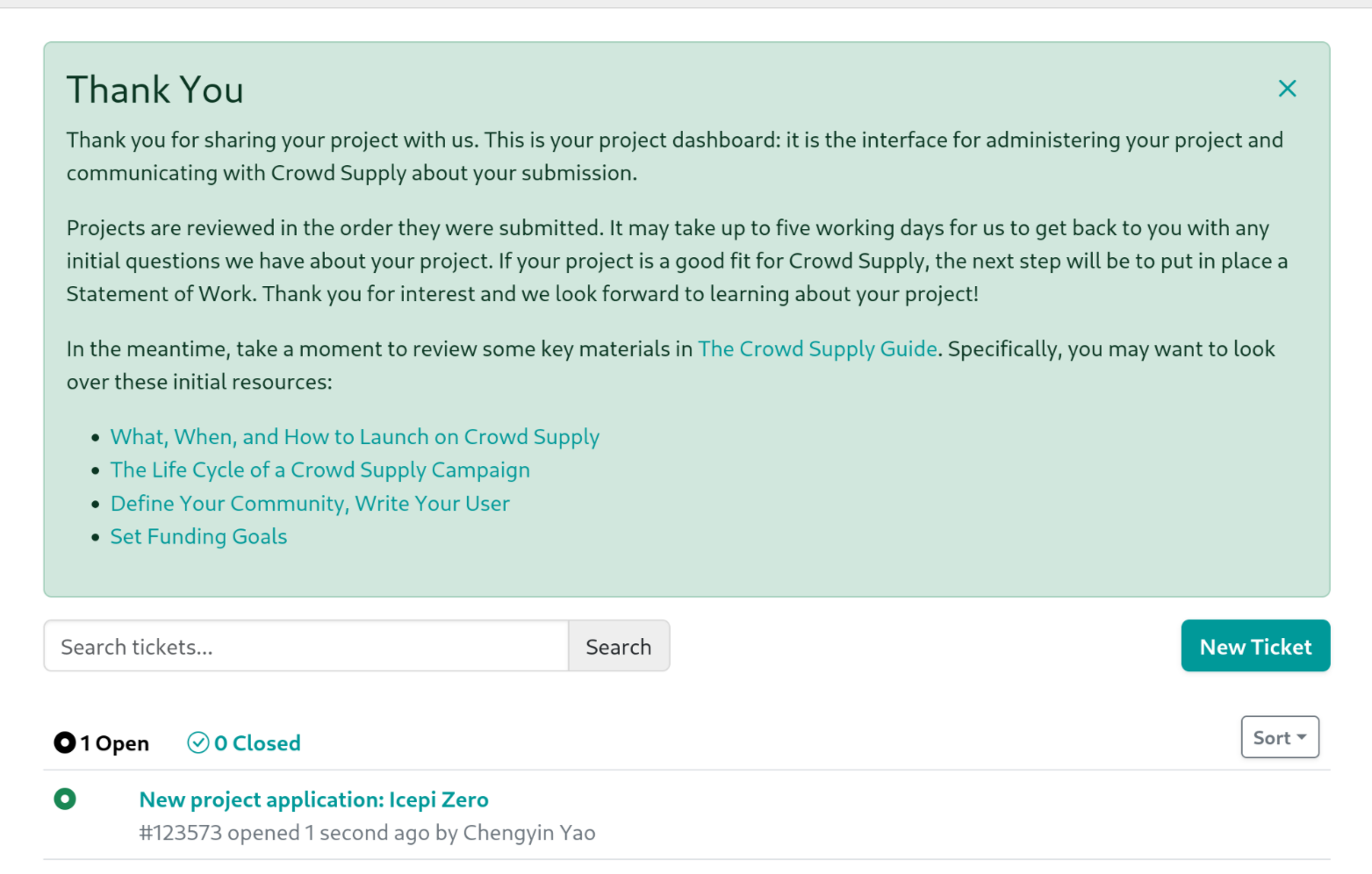

3. Submitted icepi zero to crowdsourcing :)

4. Got hackaday post https://hackaday.com/2025/05/29/icepi-zero-a-pi-zero-for-fpga/

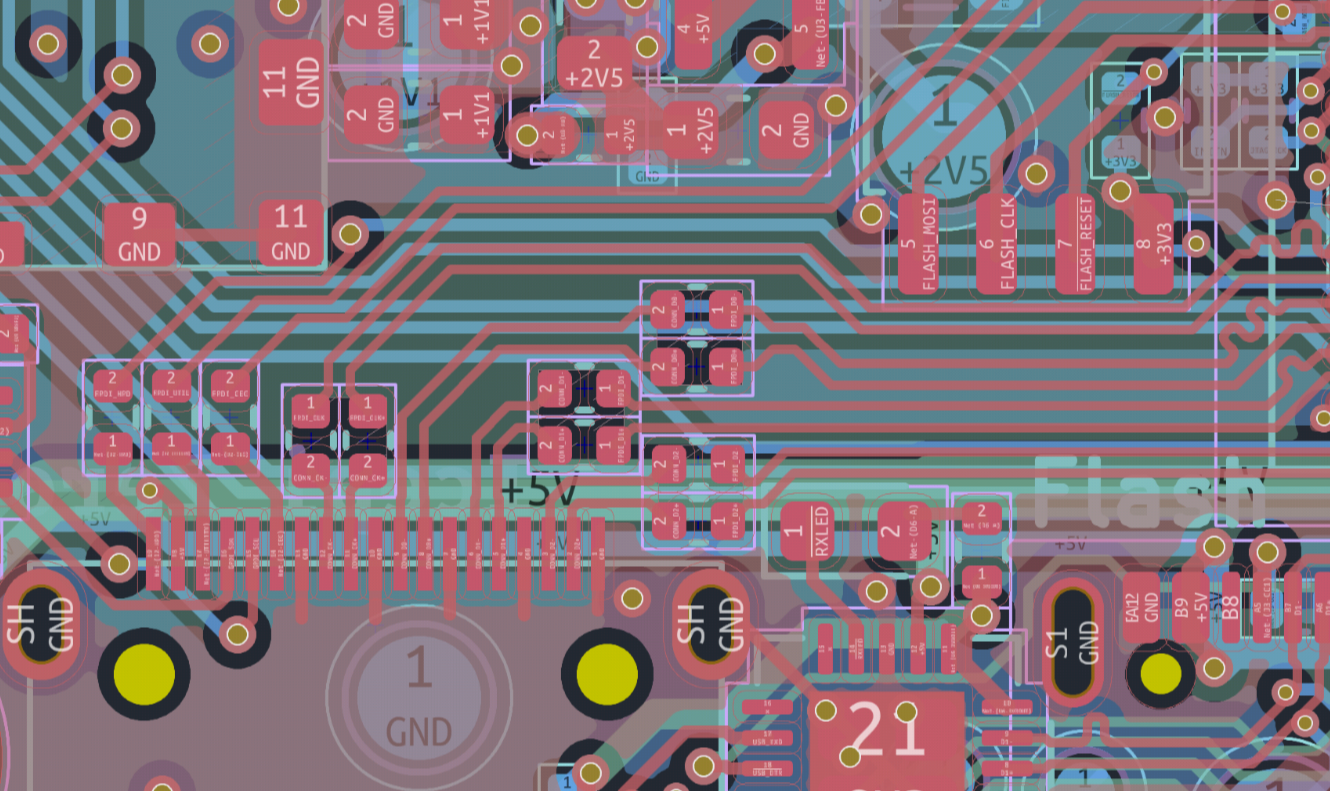

Routed a few USB I/O configured pull resistors - had like no space left...

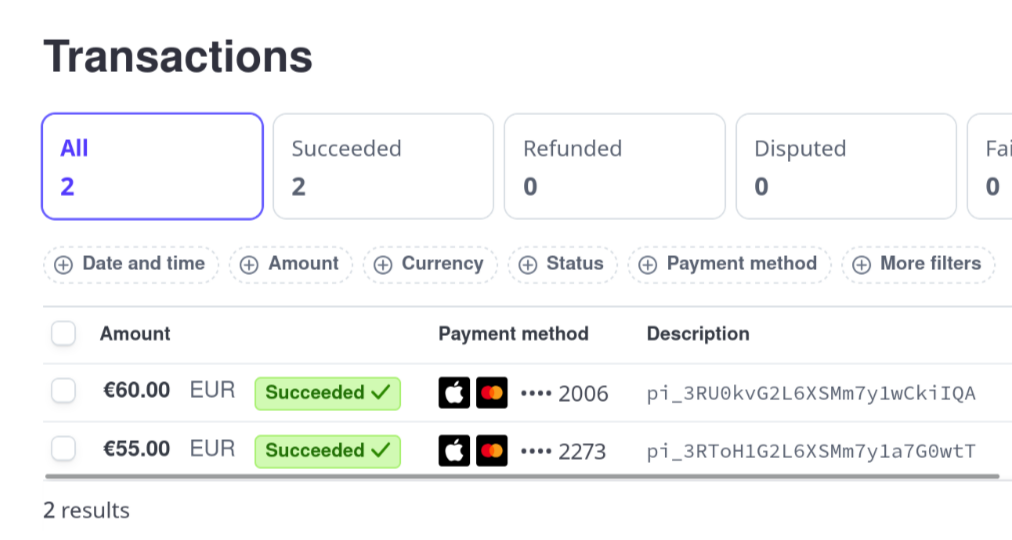

Sold 2 icepi zeros :O

Added a memtest example, also advertised a lot on reddit & co.

Polished the readme and shipped the project! Multiple reddit communities like this one: https://www.reddit.com/r/embedded/comments/1kwx5p7/i_built_the_fpga_raspberry_pi_zero_equivalent/

Successfully implemented a UART module! Includes the receiver and transmitter: Currently it just deserializes the data, then re-serializes the data to send it back via usb uart (The FTDI chip)

But this isn't the standard Arduino uart code - it's implemented in the hardware level (think about w/ transistors)

https://github.com/cheyao/icepi-zero/commit/c4abb07bcfd9b90a4741b2cbd0cf13a63da69339

Switched to make build system ;D

Got HDMI working!!!! This thing was a hell to compile. Tried to compile a core afterwards but failed lol - didn't have enough patience

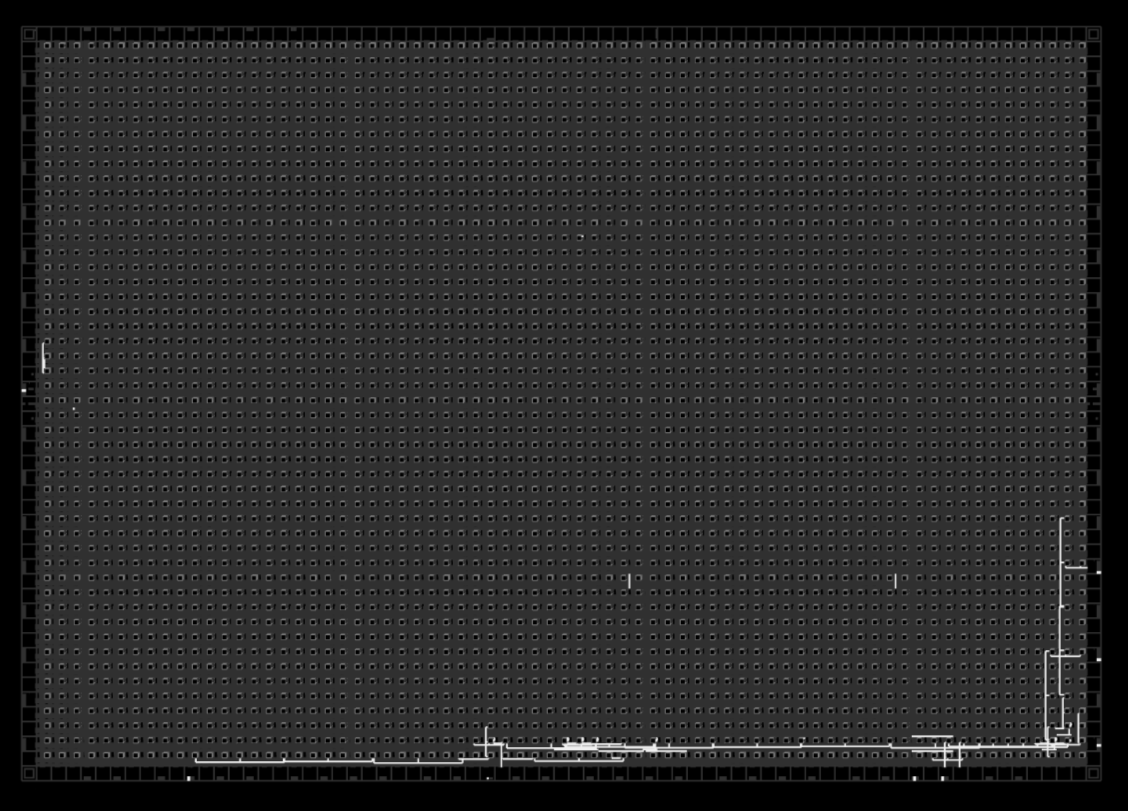

Made a custom built version of nextptr: Had to use gcc because clang didn't have embed, and this wasnt documented anywhere sob

Anyways I made the custom version just to get this image: An image representation of the insides of the fpgas. All white lines are physical connections and the white squares are configured LUTs (think of them of slightly more advanced logic gates)

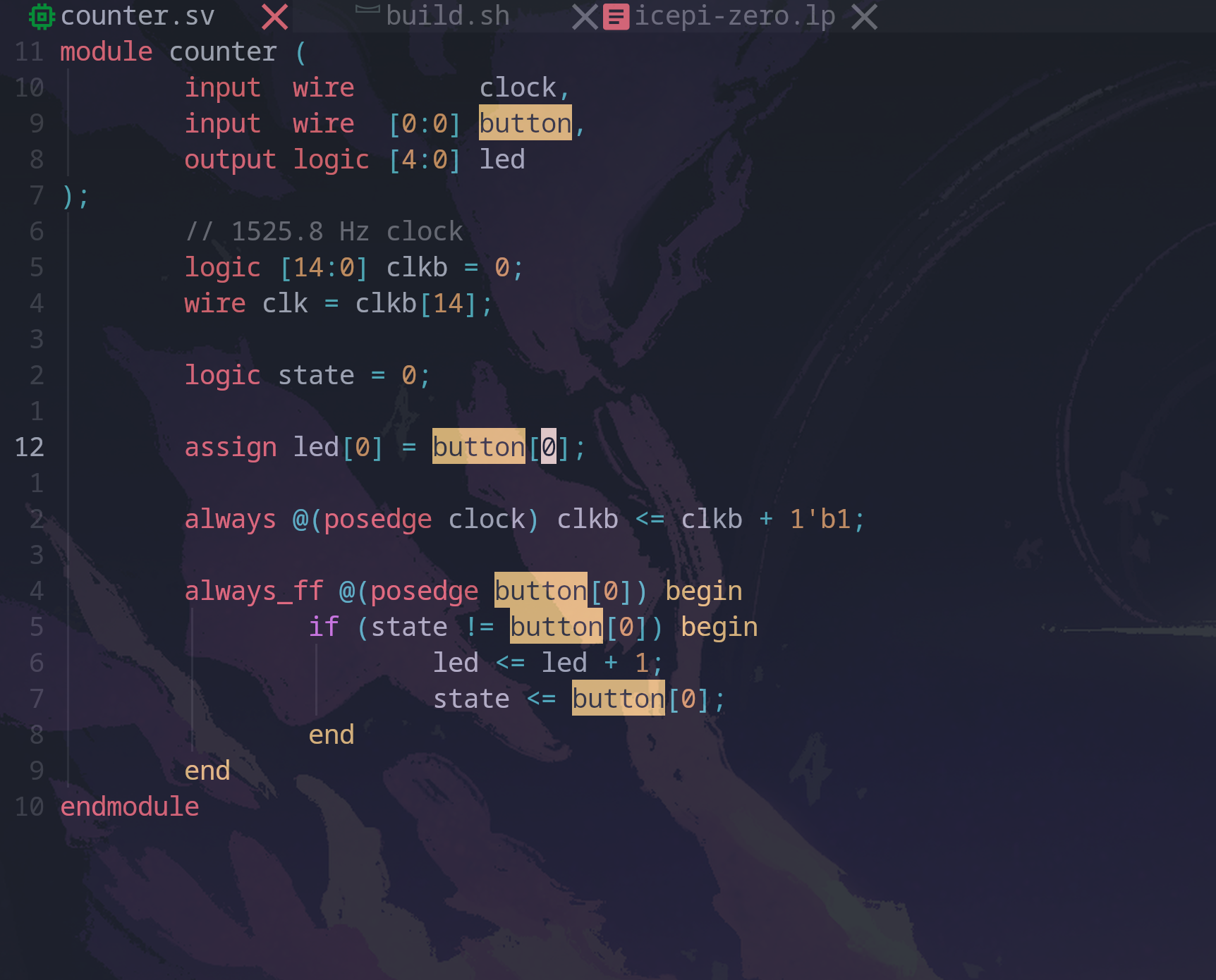

Now the button is an counter! Didn't know it would be so hard - fixed another lpf bug, and made multiple verilog revisions. Yosys is so unhelpful when the code isn't synthesable

Just got the button -> led to work! Turns out it's that yosys will automatically unpack arrays with a length of 0 into a single wire, and that will cause the lpf assignment to fail. But nexptr won't report this assignment fail...

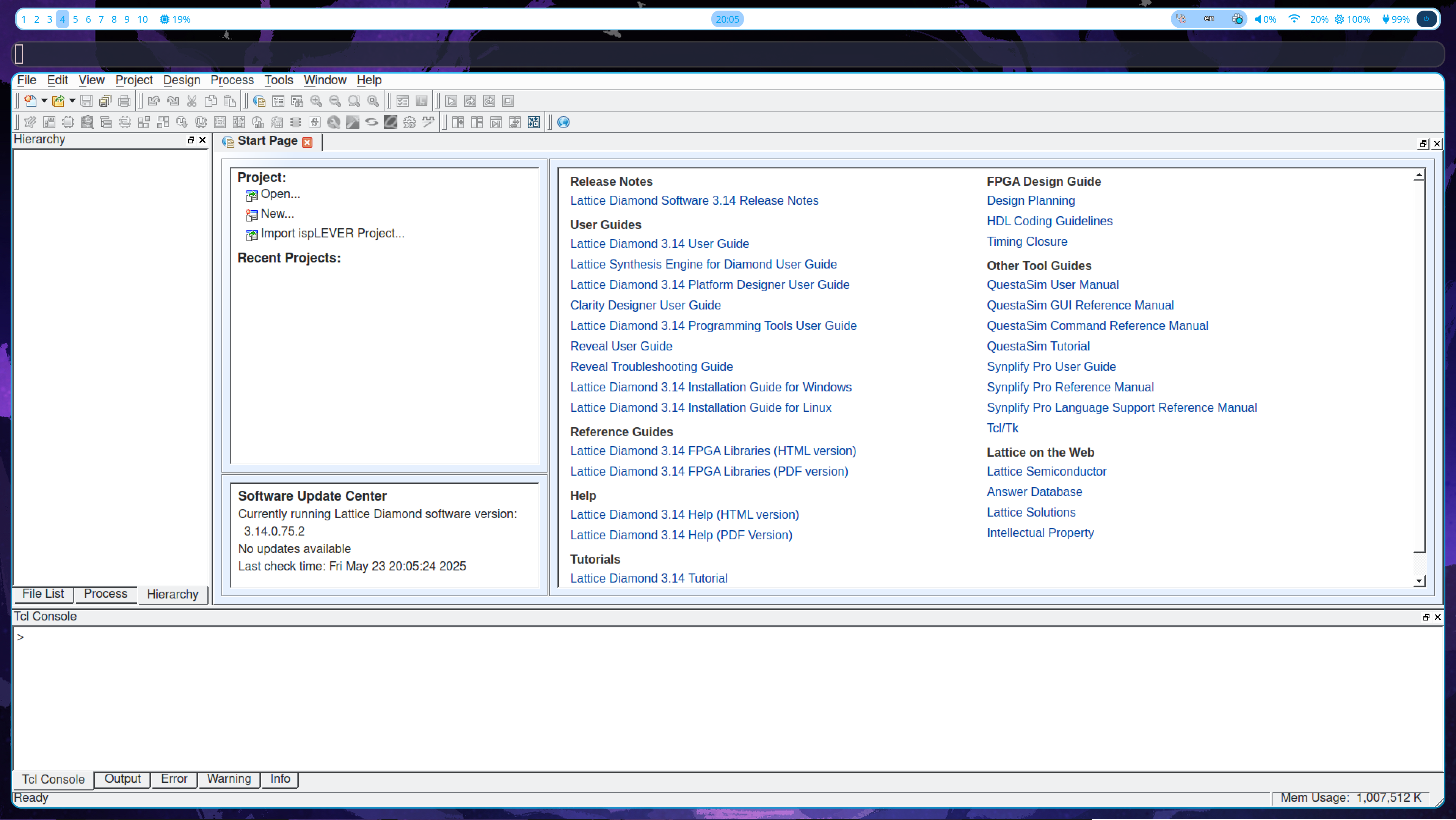

Succeeded at downloading the official ecp5 programming tool! It's fucking legacy stuff but I need to test if the pullups are broken

tried to make a counter module but on the hardware it didn't work,,,, I'm debugging it tomorrow.

I suspect it's a bad lpf pin

Got mr. blinky to work!!! Had to setup a whole toolchain because fpgas are so undocumented :sob:

Also made a pr to openfpgaloader! https://github.com/trabucayre/openFPGALoader/pull/553

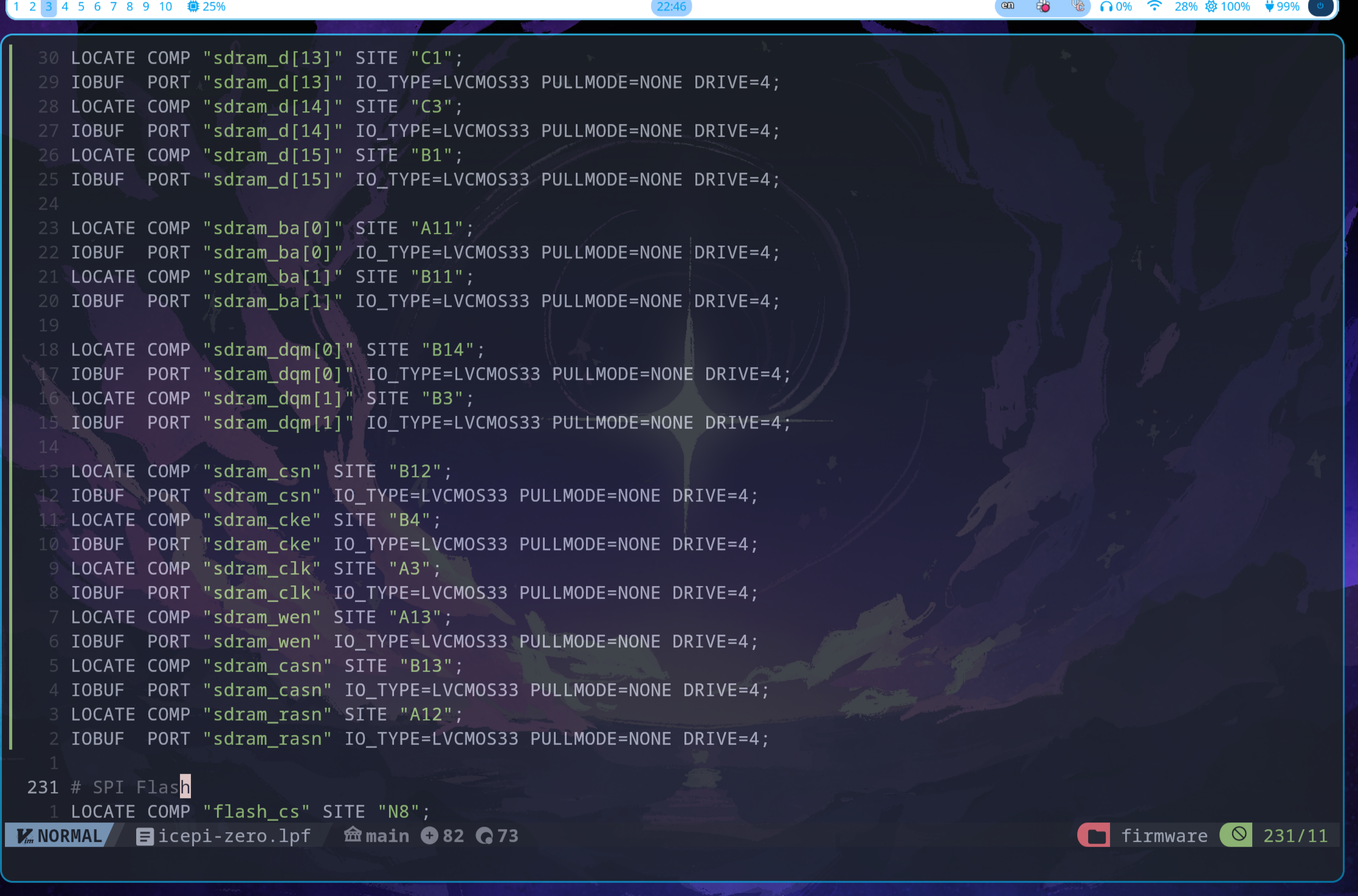

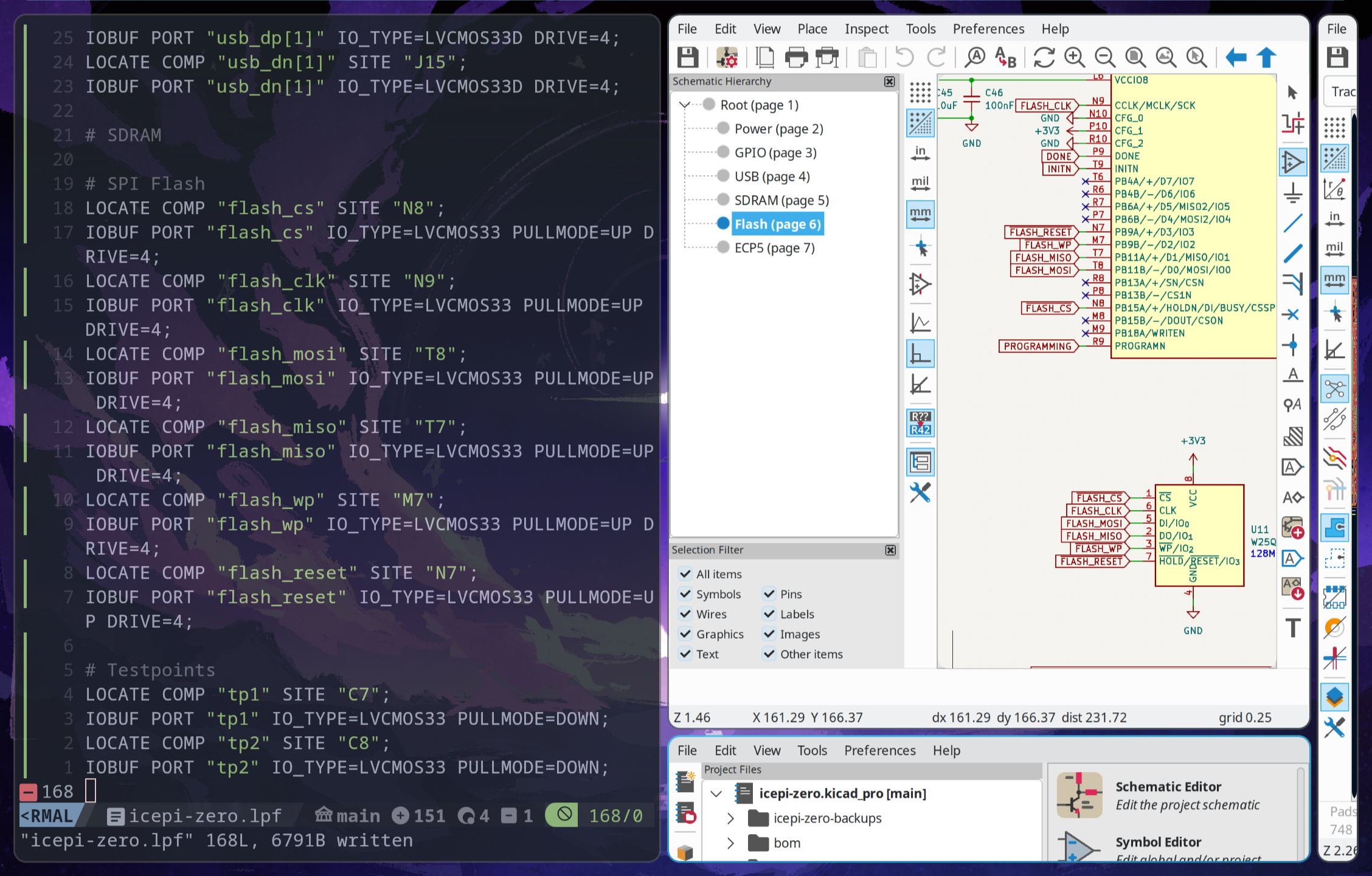

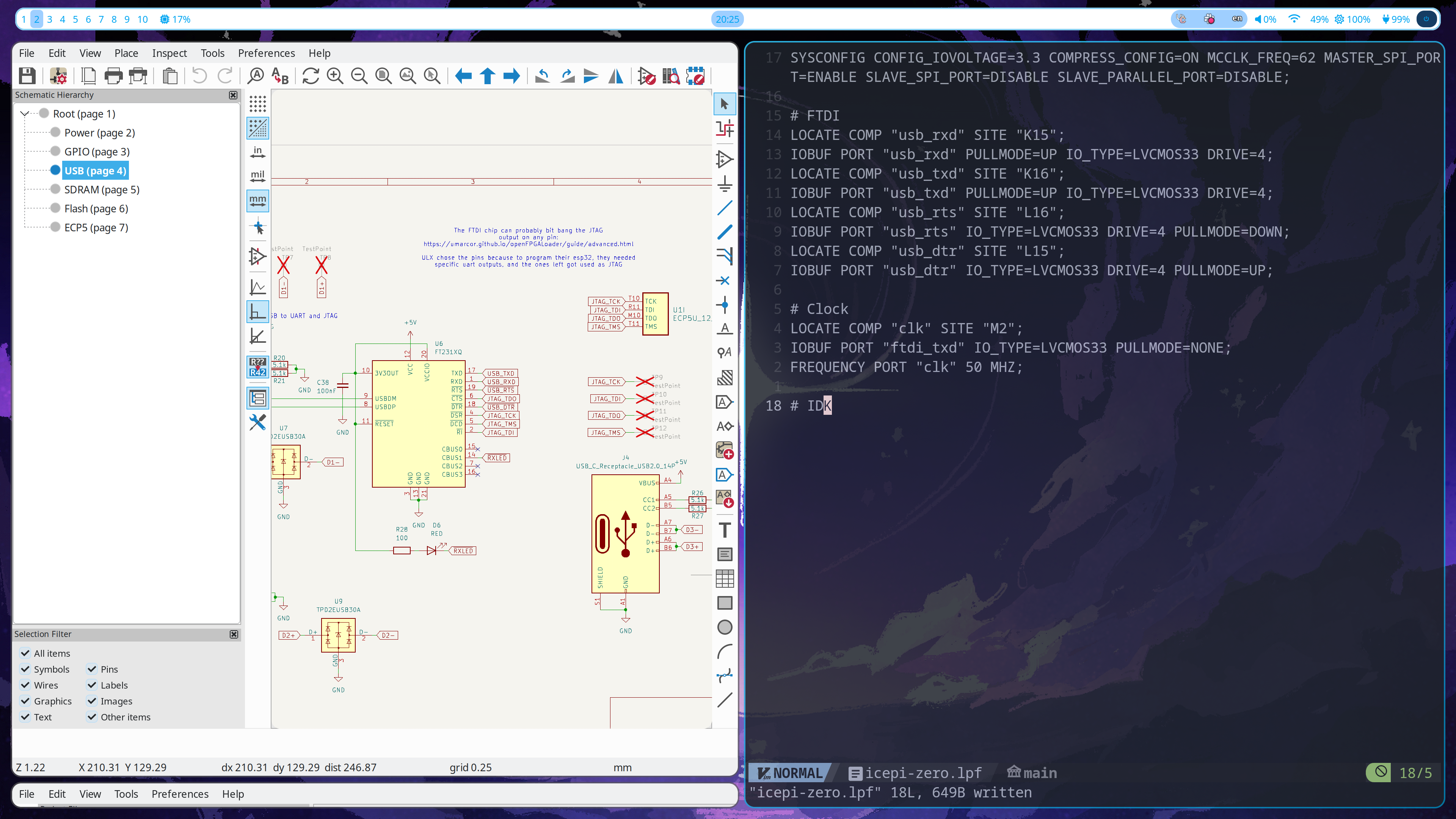

Finished the f lpf file!!! Added another 100+ lines of pinout, manually browsing the schematic is becoming so painful.

But good news: I also prettified the schem! :D

Added 100+ lines to the lpf file while reverse engineering the io format.

Crawled through my schematic & pcb editor to find all the pins.

Also fixed multiple typos on the schematic :sob:

Started writing the lpf file for my icepi-zero. It involves a large amount of schematic browsing and googling since this format is quite cryptic.

A lpc basically maps physical pins to virtual pins, while configuring the pin's capabilities.

I've changed the one button on the back to two of them. Then moved a lot of traces & vias around by small amounts to ensure the ground plane continuity and better manufaturability. Also finished tuning all the traces

Impedance matched USB & HDMI's traces according to the JLCPCB's 4 layer stackup, and started experimenting w/ kicad's auto length tuning

That’s amazing! congratulations